JTAG

JTAG(ジェイタグ Joint Test Action Group)は,ICの検査・プリント基板の検査・デバッグなどに使える機能で,バウンダリスキャンテストやテストアクセスポートの標準化の通称。

ICがどんどん高度化されてきて,ピン間隔も狭く細くなり,テストのためのプローブを使っての検査は非常に困難になってきた。BGAなどのICでは,もはや不可能。

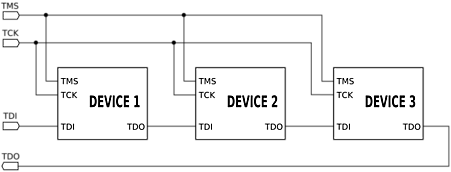

このため,検査時にIC内部の回路を数珠つなぎにして順番に読み出す仕組みが考え出された。これをバウンダリスキャンテスト(boundary scan test)と言っているらしく,その仕様を規格化したのがJTAG。1990年に,IEEE1149.1として標準化されている。

IEEE1149.1で規格化されたJTAGのインターフェース仕様は,

- TDI (Test Data In)

デバイスのテストまたはプログラミングロジックに送るデータ。

デバイスが正しい状態にある場合,TCKの立ち上がりエッジでサンプリングされる。 - TDO (Test Data Out)

デバイスのテストまたはプログラミングロジックから出力されるデータ。

デバイスが正しい状態にある場合,TCKの立ち下がりエッジで読み出せる。 - TCK (Test Clock)

デバイスの動作を同期させるクロック信号。 - TMS (Test Mode Select)

TCKの立ち上がりエッジでサンプリングされ,次の状態を決定する。 - TRST (Test Reset) (オプション)

デバイスをリセットする。

のような仕様になっている。

検査目的だけでなく,組み込みシステムなんかのソフトウェア・デバッグ目的で,それまで使われていたICE*1の代わりにJTAGが使われている。

いろいろな機能を実現するために,各メーカーがオプション機能やプライベート命令を使って勝手に機能を拡張している。

また,そのような拡張した機能は,半導体メーカーや高価な契約を結んだサードパーティしか知ることが出来ないようにもなっている。

このため,通常のJTAGアダプター等の機器は,その製造コストとは関係なしに非常に高価である。

JTAGのプロトコル

JTAGの規格(IEEE 1149.1)で定められているのはインターフェース仕様とごく基本の手順のみとなっている。

このため,各デバイスメーカーがプライベート命令を使ってどんどん拡張し,いろいろなオプション機能を実装している。特にCPLDやFPGAの書き込みやCPUのデバッグ機能は,すべてプライベート命令を使って実現している。

しかし,この拡張機能はデバイスメーカーが公開することは無いのが通常なので,一般人にはその使い方がよくわかりません。

デバイスプログラミングの標準化規格(IEEE1532)も一応あるにはあるが,これは全く普及していない。

| アルゴリズム層 | バウンダリスキャン(IEEE1149.1) |

| デバイスプログラミング(各デバイスメーカー非公開) | |

| CPUのデバッグ(各デバイスメーカー非公開) | |

| データリンク層 | データレジスタ/命令レジスタの操作(IEEE1149.1) |

| 物理層 | 標準規格なし(任意) |

詳細は,特殊電子回路株式会社のページを参照。

新しくコメントをつける